With the explosive growth in data center,5G communication and AI computing power demands, Serdes(Serializer/Deserializer), DSP(Digital Signal Processing),and Retimer chips, as the core components of high-speed interconnects, have become increasingly important. As communication rates surge from 100G to 400G and even higher to 1.6T,the performance of Serdes/DSP/Retimer chips directly determines the efficiency and reliability of communication systems. Therefore, conducting comprehensive and efficient testing on these chips has become a crucial step in ensuring the quality of communication systems.

Architecture and Function of Serdes/DSP/Retimer Chips

(1)Serdes Chip

Serdes chips are key modules in high-speed communication systems, responsible for converting parallel data to serial data for transmission and vice versa. They typically consist of a transmitter(Tx)and a receiver(Rx).The transmitter converts parallel data into high-speed serial signals through modulation techniques, while the receiver restores the serial signals back to parallel data through demodulation. Performance indicators of Serdes chips include transmission rate, jitter,and signal integrity, all of which directly affect the quality and reliability of data transmission.

(2)DSP Module

The DSP module is an essential part of Serdes chips, primarily used for digital signal processing. It optimizes signal quality and transmission performance through complex algorithms for equalization, filtering, and error correction. As transmission rates increase, the complexity of DSP algorithms also rises, especially in high-frequency signal transmission, where the role of DSP becomes even more critical.

(3)Retimer Chip

Retimer chips are designed to re-time signals to reduce jitter and extend signal transmission distance. They synchronize and reshape input signals through internal CDR(Clock Data Recovery)and signal regeneration modules, ensuring that signals remain high-quality after long-distance transmission. Retimer chips are widely used in data centers,5G communication, and AI computing power applications.

Testing Focus of High-Speed Digital Chips

Testing for Serdes/DSP/Retimer chips typically covers the transmitter(Tx),receiver(Rx),clock, power supply, and protocol aspects. Research and development testing, DVT(Design Verification Testing),and production testing each have different requirements and focuses.

During the research and development testing phase, industry-leading brand products are usually used as standards. For example, AWGs(Arbitrary Waveform Generators)or BERTs(Bit Error Rate Testers)that comply with IEEE standards and have jitter and crosstalk injection functions, as well as high-frequency insertion loss boards, are used to verify the CDR and receiver equalization capabilities of Serdes/DSP/Retimer chips. Oscilloscopes with standard specification analysis functions (such as IEEE and PCIe standards)are used to analyze the Tx eye diagram signal quality, multi-channel consistency, and verify the FIR(Finite Impulse Response)algorithm. These R&D tests focus more on product compliance, with strict precision requirements for test equipment, making products from first-tier instrument manufacturers the preferred choice.

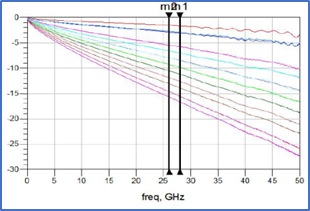

When cost becomes a consideration, Te-lead Technologies can provide some low-cost, high-precision products for Serdes/DSP/Retimer chip customers to choose from. For example, the custom-designed 112G high-frequency insertion loss board by Te-lead Technologies can provide linear insertion loss changes under various lengths of traces, offering reliable hardware support for chip testing.

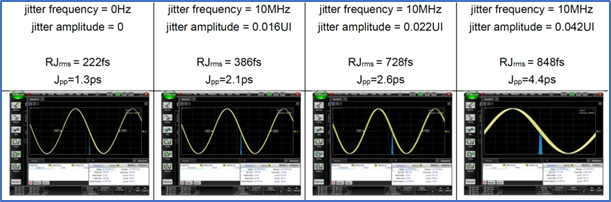

In terms of clock signals, the CLK20 jitter injection clock source can provide clock outputs ranging from 78.125MHz to 20GHz and can inject sinusoidal modulation signals with FM from 1KHz to 80MHz and AM from 0.01 to 17UI into the clock. These typical signals can be used to inject into the chip clock to verify its CDR tolerance capability. In addition, Te-lead Technologies also offers a complete set of products related to high-frequency clock processing, such as frequency division, multiplication, and multi-channel clock distribution, providing more testing options for Serdes/DSP/Retimer chip manufacturers.

However, considering efficiency and cost, it is impractical to use R&D-type test equipment in DVT or large-scale production testing. As the number of chip channels increases, compact synchronous measurement of multiple channels becomes crucial.

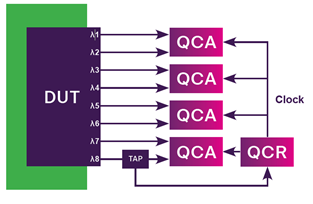

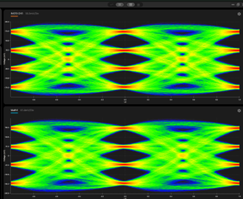

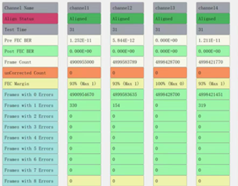

To address this, Te-lead Technologies has launched the QCA1002 ultra-low jitter (Jrms 150fs,1.0mVRMS) electrical sampling oscilloscope and the QCR1002 electrical clock recovery instrument with 4-port triggering. This equipment configuration is the most compact in the industry and is ideal for production testing. Four QCA1002 units paired with one QCR1002 can synchronously measure the performance of 8 pairs Line Tx channels of Serdes/DSP/Retimer chips in PRBS(Pseudorandom Binary Sequence)mode and obtain relevant eye diagram parameters required by the IEEE standard, such as eye height(EH),eye width(EW),and receiver linearity(RLM).Thanks to the precise time base of the QCA1002,the measured signal traces are very clear, and the signal quality is comparable to that of first-tier brands, making it easier to distinguish marginal chips.

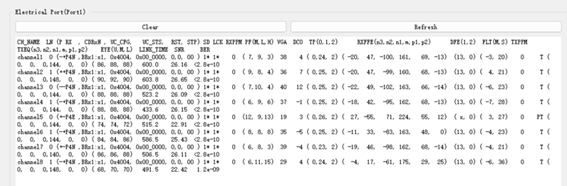

In addition to testing the Tx performance of Serdes in PRBS mode using an oscilloscope+clock recovery instrument, the signal processing capabilities of Host Tx and Line Tx are also typically measured. For example, an external signal source(such as Te-lead Technologies's VIT8X00)can be used as the Host input, feeding its 8 pairs of differential signals into the Host Tx end of the DSP chip, and then using the same QCA1002+QCR1002 configuration to measure the eye diagram results, thereby verifying the equalization and recovery capabilities of Line Tx. The VIT8X00 can fine-tune the output to meet the IEEE Host standard's limit signals, a function of great significance in chip production testing.

Of course, production testing of Serdes/DSP/Retimer chips is not limited to Tx performance; Rx performance testing is also an essential part. The chip's Rx includes Line Rx and Host Rx, with the key focus being on verifying the equalization and recovery capabilities of Rx. Te-lead Technologies' VIT8X00 series bit error rate tester can simulate output signals with different loss amplitudes and adjust clock offsets. By feeding these set signals into Line Rx and Host Rx and connecting the output signals to the error detection port of the VIT8X00, the bit error rate and FEC(Forward Error Correction)margin can be obtained. At the same time, the VIT8X00 can also monitor performance indicators such as eye height, signal-to-noise ratio(SNR), and FFE(Finite Impulse Response Filter),thereby more accurately obtaining the performance characteristics of Rx.

In addition, the production testing of Serdes/DSP/Retimer chips also involves testing of power consumption,I2C, control, and other signals. Traditional ATE(Automated Test Equipment)test systems can basically meet these needs. For the high-speed part, Te-lead Technologies' electro-optic sampling oscilloscope and multifunctional bit error rate tester can be utilized. Te-lead Technologies can also provide corresponding API files for system integration. During the actual signal input and output process, many complex issues such as probe cards, RF interfaces, cable assemblies, software de-embedding, and calibration are involved, and Te-lead Technologies can also provide corresponding solutions to help customers efficiently complete chip testing.

Te-lead Technologies has many years of experience in sales and technical services of high-speed signal test instruments and fixtures . It can create standard and customized product test solutions according to customer needs.